此圖是從intel datasheet:Intel64 and IA-32 Architectures Software Develops Manual Volume3A所截取下來,從這張圖就可知道CPU如何在各模式之間切換;及為什麼可以作到向下相容的架構。

圖二

圖二 圖一

圖一AMD公司設計,可以在同一時間內處理64位的整數運算,並兼容于X86-32架構。其中支持64位邏輯定址,同時提供轉換為32位定址選項;但數據操作指令默認為32位和8位,提供轉換成64位和16位的選項;支持常規用途暫存器,如果是32位運算操作,就要將結果擴展成完整的64位。這樣,指令中有“直接執行”和“轉換執行”的區別,其指令字段是8位或32位,可以避免字段過長。

x86-64(也叫AMD64)的產生也並非空穴來風,x86處理器的32bit尋址空間限制在4GB內存,而IA-64的處理器又不能兼容x86。AMD充分考慮顧客的需求,加強x86指令集的功能,使這套指令集可同時支持64位的運算模式,因此AMD把它們的架構稱之為x86-64。在技術上AMD在x86-64架構中為了進行64位運算,AMD為其引入了新增了R8-R15通用暫存器作為原有X86處理器暫存器的擴充,但在而在32位環境下並不完全使用到這些暫存器。原來的暫存器諸如EAX、EBX也由32位擴張至64位。在SSE單元中新加入了8個新暫存器以提供對SSE2的支持。暫存器數量的增加將帶來性能的提升。與此同時,為了同時支持32和64位代碼及暫存器,x86-64架構允許處理器工作在以下兩種模式︰Long Mode(長模式)和Legacy Mode(傳統模式),Long模式又分為兩種子模式(64bit模式和Compatibility mode兼容模式)。該標準已經被引進在AMD伺服器處理器中的Opteron處理器。

而今年也推出了支持64位的EM64T技術,再還沒被正式命為EM64T之前是IA32E,這是英特爾64位擴展技術的名字,用來區別X86指令集。Intel的EM64T支持64位sub-mode,和AMD的X86-64技術類似,採用64位的線性平面尋址,加入8個新的通用暫存器(GPRs),還增加8個暫存器支持SSE指令。與AMD相類似,Intel的64位技術將兼容IA32和IA32E,只有在營運64位作業系統下的時候,才將會採用IA32E。IA32E將由2個sub-mode組成︰64位sub-mode和32位sub-mode,同AMD64一樣是向下兼容的。Intel的EM64T將完全兼容AMD的X86-64技術。現下Nocona處理器已經加入了一些64位技術,Intel的Pentium 4E處理器也支持64位技術。

應該說,這兩者都是兼容x86指令集的64位微處理器架構,但EM64T與AMD64還是有一些不一樣的地方

AMD的K8不是真正的64bit處理器,其和Intel的EM64T處理器一樣,不是真正的64bit處理器。Microsoft的WINXP64bit也不是真正意義上的64bit作業系統。真正64bit系統(硬體和軟體系統)出來的時候,現下這些所謂的64bit全部會淘汰,而這段時間會相當長,至少三年內難以實現;況且配件的更新速度很快,只要用的順手,何必在意以後會怎樣。順便說一下,現下的K8實際上是40bit處理器,而非64bit處理器;EM64T實際上是32bit處理器,只是在物理內存尋址上擴展到36bit。

AMD64 及 EM64T 倒底誰是一顆真正的 64 bit處理器,不用太在意, 這兩者都是由 32bit 處理器改進而來, 前陣子在 bbs 的 hardware 版, 為了AMD64 是不是創新的架構, 爭論了許久. 不過, 實際使用上, AMD64 不論是要當 32bit或 64 bit處理器來用, 算是不錯, 效能好, 溫度又低!

x86-64(也叫AMD64)的產生也並非空穴來風,x86處理器的32bit尋址空間限制在4GB內存,而IA-64的處理器又不能兼容x86。AMD充分考慮顧客的需求,加強x86指令集的功能,使這套指令集可同時支持64位的運算模式,因此AMD把它們的架構稱之為x86-64。在技術上AMD在x86-64架構中為了進行64位運算,AMD為其引入了新增了R8-R15通用暫存器作為原有X86處理器暫存器的擴充,但在而在32位環境下並不完全使用到這些暫存器。原來的暫存器諸如EAX、EBX也由32位擴張至64位。在SSE單元中新加入了8個新暫存器以提供對SSE2的支持。暫存器數量的增加將帶來性能的提升。與此同時,為了同時支持32和64位代碼及暫存器,x86-64架構允許處理器工作在以下兩種模式︰Long Mode(長模式)和Legacy Mode(傳統模式),Long模式又分為兩種子模式(64bit模式和Compatibility mode兼容模式)。該標準已經被引進在AMD伺服器處理器中的Opteron處理器。

而今年也推出了支持64位的EM64T技術,再還沒被正式命為EM64T之前是IA32E,這是英特爾64位擴展技術的名字,用來區別X86指令集。Intel的EM64T支持64位sub-mode,和AMD的X86-64技術類似,採用64位的線性平面尋址,加入8個新的通用暫存器(GPRs),還增加8個暫存器支持SSE指令。與AMD相類似,Intel的64位技術將兼容IA32和IA32E,只有在營運64位作業系統下的時候,才將會採用IA32E。IA32E將由2個sub-mode組成︰64位sub-mode和32位sub-mode,同AMD64一樣是向下兼容的。Intel的EM64T將完全兼容AMD的X86-64技術。現下Nocona處理器已經加入了一些64位技術,Intel的Pentium 4E處理器也支持64位技術。

應該說,這兩者都是兼容x86指令集的64位微處理器架構,但EM64T與AMD64還是有一些不一樣的地方

AMD的K8不是真正的64bit處理器,其和Intel的EM64T處理器一樣,不是真正的64bit處理器。Microsoft的WINXP64bit也不是真正意義上的64bit作業系統。真正64bit系統(硬體和軟體系統)出來的時候,現下這些所謂的64bit全部會淘汰,而這段時間會相當長,至少三年內難以實現;況且配件的更新速度很快,只要用的順手,何必在意以後會怎樣。順便說一下,現下的K8實際上是40bit處理器,而非64bit處理器;EM64T實際上是32bit處理器,只是在物理內存尋址上擴展到36bit。

AMD64 及 EM64T 倒底誰是一顆真正的 64 bit處理器,不用太在意, 這兩者都是由 32bit 處理器改進而來, 前陣子在 bbs 的 hardware 版, 為了AMD64 是不是創新的架構, 爭論了許久. 不過, 實際使用上, AMD64 不論是要當 32bit或 64 bit處理器來用, 算是不錯, 效能好, 溫度又低!

由 Intel EM64T 技術談 64 位元 CPU

由於軟體的功能越來越強大且多元化,所消耗的系統資源相對的也越多,因此在軟體的功能不斷提升的同時,硬體的處理能力也就捉襟見拙。而新技術不斷的發展,除了代表科技的進步外,也因應這必然的趨勢,造就了電腦平台的變革 —DDRⅡ、PCI Express、Hyper Threading 與 EM64T 等。

由於軟體的功能越來越強大且多元化,所消耗的系統資源相對的也越多,因此在軟體的功能不斷提升的同時,硬體的處理能力也就捉襟見拙。而新技術不斷的發展,除了代表科技的進步外,也因應這必然的趨勢,造就了電腦平台的變革 —DDRⅡ、PCI Express、Hyper Threading 與 EM64T 等。

一、何謂 64 位元 CPU我們知道一個功能強大的軟體其實是由無數行的程式所組合而成,每一行的程式碼均會透過編譯器編譯成數筆資料,送到 CPU 內部的暫存器中等待執行。而所謂的 64 位元也就是在這資料的寬度、暫存器的大小以及執行指令的長度均為 64 位元,另外在記憶體的定址能力同樣也為 64 位元。

二、64 位元 CPU 的發展Intel CPU 的發展從 80386 之後便演進為 32 位元,到 1994 年 Intel 與 HP 共同開發 VLIW(Very Long Instruction Word)架構的 Itanium、Itanium2 的 IA-64 CPU,希望能將 HP 的 PA-RISC、COMPAQ 的 Alpha 以及 x86 架構的 PC 作一整合,以期降低研發高階伺服器處理器成本,並能跨平台的執行不同的作業系統。只是因為 Itanium、Itanium2 的 CPU 使用的是 VLIW 架構,雖然在執行 64 位元的作業系統與應用程式非常順暢,但於 32 位元的作業系統與應用程式中必須透過指令轉譯的方式來執行,導致在 32 位元的環境下效能不彰,因此發展上是叫好不叫座。在 64 位元 CPU 沈潛好一段時間之後,AMD 於 2003 年四月推出 64 位元 x86 架構的處理器 Opteron,以及 Apple 推出 PowerPC G5 的 RISC CPU,既可以執行 64 位元作業系統與應用程式,亦可向下相容於原本 32 位元的作業系統與應用程式,一時間 64 位元處理器的話題又熱絡起來。而 Intel 為了不讓競爭對手專美於前,於 2004 年春季 IDF 論壇中發表了 Intel 64bit Extension Technology 的新技術,並於 4 月份正式定名為 Intel Extended Memory 64 Technology(EM64T),並採用被稱之為 IA-32e 的新操作模式。

三、EM64T 技術Intel EM64T 是為了強化 IA-32 架構所發展的新技術。包含此技術的 IA-32 處理器除了可向下相容於現存的 32 位元軟體,並賦予軟體存取更多記憶體空間。並且允許那些開發於 32 位元定址模式下的軟體擁有執行於 64 位元定址空間的能力。相較於之前 IA32,擁有 EM64T 的 IA32e 最大的不同是將記憶體定址能力由原本 2 的 32 次方提升到 2 的 64 次方,也就是 18446744TB。

四、包含 EM64T 技術處理器的執行模式包含 IA32e 的處理器可執行在 Legacy IA-32 Mode 與 IA-32e Mode。IA-32e Mode 又包含了兩種子模式:1. Compatibility Mode:允許 64 位元的作業系統在不做任何的變動下執行大多數原生的 32 位元軟體。2. 64-bit Mode:允許 64 位元作業系統執行那些存取 64 位元位址空間的應用程式。

五、64-bit Mode 是用來在 64 位元作業系統下執行 64 位元應用程式,包含下列幾項特性:● 64 位元線性定址。● 8 個全新的一般暫存器(General-Purpose Register)。● 8 個全新 Streaming SIMD Extensions(SSE)暫存器支援 SSE、SSE2與SSE3。● 64 位元寬度的 GPR 與指令指標● 相同的 byte-register addressing● 更快速的中斷優化機制● 全新的指令指標相對定址模式64-bit Mode 可透過 64 位元作業系統藉由分割程式碼的準則來啟動。初始定址大小為 64 位元,初始運算元大小為 32 位元。

六、在 Compatibility Mode 中,絕大部分的 16 位元或 32 位元應用程式均可在不重新編譯的狀況下執行於 64 位元作業系統中。相同於 64-bit Mode,Compatibility Mode 可透過 64 位元作業系統藉由分割程式碼的準則來啟動。也就是說在同一時間中,64 位元應用程式也可被執行於 64-bit Mode,而不需重新編譯。

七、Legacy IA-32 Mode 包含保護模式、真實位址模式或是虛擬 8086 模式。針對這些模式撰寫的軟體,EM64T 的處理器均有完整的相容性。

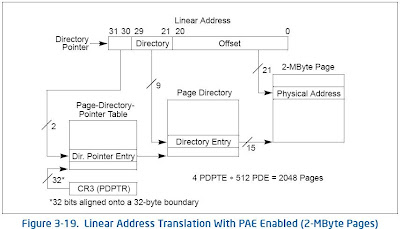

上圖一列出 EM64T 處理器在不同模式下的差異:

上面圖二列出了在不同模式中所支援的暫存器類別:

八、64 位元處理器的迷思是不是購買了 64 位元處理器,相對的執行速度就是原本 32 位元的兩倍?其實以目前的作業系統 Windows XP 或是 Windows 2000 均為 32 位元的作業系統,而應用程式部分亦為 32 位元,也因此在程式碼分割與執行指令上仍為 32 位元寬,而 CPU 資料處理部分仍為 32 位元,也因此與目前的 IA-32 處理器並無差別。在未來 Windows XP 64-bit Edition for Extended System 上市後搭配 64 位元的應用程式,在效能方面才能有所提升。